# JVC

# SERVICE MANUAL

### DIGITAL STILL CAMERA

## GC-QX3U

#### **SPECIFICATIONS**

Dimensions : 108 (W) mm x 64 (H) mm x 57 (D) mm

(4-5/16" x 2-9/16" x 2-1/4")

: 4.0 W (when the LCD screen is off) Power consumption 5.6 W (when the LCD screen is on)

> : Approx. 290 g (0.64 lbs) (without a Memory card and battery)

: DC 5 V == Power source

Weight

: Built-in Flash

Auto/red-eve prevention/forced/disabled

Recommended distance for flash : 2.3 m to 5.2 m

: 2.0 inch, cool polysilicon TFT, 200,000 pixels

: SmartMedia<sup>TM</sup> 3.3V (up to 64MB) Storage media CCD

: 3.34 million pixels (3.24 million valid pixels), 1/1.8" square pixels, primary color filter, interlace scan CCD

: 2032 x 1536 (TIFF 9.5MB, FINE 1MB, STD 700KB) 1024 x 768 (TIFF 2.4MB, FINE 500KB, STD 300KB) Recording pixels

640 x 480 (TIFF 980KB, FINE 150KB, STD 80KB)

Focal distance : 7.5 mm to 17.5 mm

(equivalent to 37mm to 86 mm on a 35 mm still camera)

Lens : 2.3X optical zoom lens

Video : 160 x 120, 20 seconds (80KB - 200KB) JVC original : Exif Ver. 2.1 (DCF compliant), TIFF (Uncompressed), Recording format

DPOF-compatible

Sensitivity : 80/160/320 (ISO compliant) Iris value (F value) : F2.8/3.8, 5.6, 8, 11 Exposure control : Program AE, iris priority AE : +/-2EV (0.5EV steps) **Exposure compensation**

Minimum subject distance : Approx. 2 cm to 50 cm (in Macro mode)

Light measurement system : Multi, spot Shutter type : Electronic shutter

Shutter speed : Auto (Program AE: 1/8 - 1/750, Iris priority AE: 1/4 - 1/750)

White balance : Auto/Manual (\*, \*, \*, \*, MWB)

Focus : Auto/Manual Self timer : 1 second, 8 seconds

Photo quality : 3 modes (STANDARD/FINE/NO COMP.) Number of storable photos : 2032 x 1536: approx. 10/8/0

(with an 8MB Memory card, STANDARD/FINE/NO COMP.) 1024 x 768: approx. 43/32/3 640 x 480: approx. 87/65/9

Battery

Printer connector : Output for optional printer

VIDEO output connector : Two-pole plug, 3.5 mm diameter (NTSC)

: Lithium ion battery

: Mini-USB connector Digital output connector

#### AC Power Adapter/Charger AA-V37

Power requirement

U.S.A. and Canada : AC 120 V ~, 60 Hz

: AC 110 V − 240 V ∼, 50 Hz/60 Hz Other countries

: 23 W Power consumption

Output

Charge : DC 3.6 V ==, 0.77 A Camera : DC 5.0 V ==, 1.5 A : 0°C to 40°C (32°F to 104°C) Operating temperature

[when charging: 10°C to 35°C (50°F to 95°F)]

: 68 (W) mm x 38 (H) mm x 110 (D) mm Dimensions (2-11/16" x 1-1/2" x 4-3/8")

: Approx. 230 g (0.51 lbs) (without a DC cord) Weight

E. & O. E. Design and specifications subject to change without notice.

#### **TABLE OF CONTENTS**

| Sect  | tion Title                                          | e                   | Page | Section                                                                            | Tit                                                 | tle                                                                         | Page               |

|-------|-----------------------------------------------------|---------------------|------|------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|--------------------|

| Impo  | ortant Safety Precautions                           |                     |      |                                                                                    |                                                     |                                                                             |                    |

| 1. DI | SASSEMBLY                                           |                     |      | 4. PARTS LIST                                                                      |                                                     |                                                                             |                    |

| 1.1   | BEFORE ASSEMBLY AND DI                              | SASSEMBLY           | 1-1  |                                                                                    | D ACCESSORY                                         | ASSEMBLY <m1></m1>                                                          | 4-1                |

|       | .1 Precautions                                      |                     |      | 4.2 OP BLOCK A                                                                     | SSEMBLY <m3< td=""><td>&gt;</td><td> 4-2</td></m3<> | >                                                                           | 4-2                |

|       | .2 Assembly and disassembly                         |                     |      | 4.3 FINAL ASSEM                                                                    | ИВLY <m2></m2>                                      |                                                                             | 4-3                |

|       | .3 Disconnection of Connecto                        |                     |      | 4.4 ELECTRICAL                                                                     | PARTS LIST                                          |                                                                             | 4-6                |

|       | TOOL AND EQUIPMENTS REQU                            |                     |      | MAIN BOAR                                                                          | ASSEMBLY <                                          | 01>                                                                         | 4-6                |

| 1.2.  | .1 Tools required for adjustme                      | ents                | 1-2  | CCD BOARD                                                                          | ASSEMBLY <0                                         | 2>                                                                          | 4-11               |

|       | DISASSEMBLY /ASSEMBLY                               |                     |      | MONI REG B                                                                         | OARD ASSEME                                         | 3LY <03>                                                                    | 4-12               |

| 1.3.  | .1 Disassembly flow chart                           |                     | 1-2  | JACK BOARD                                                                         | ASSEMBLY <                                          | 04>                                                                         | 4-14               |

| 1.3.  | .2 Disassembly method (I)                           |                     | 1-3  | STOROBE FL                                                                         | ASH BOARD A                                         | SSEMBLY <05>                                                                | 4-15               |

| 1.3.  | .3 Disassembly method (II)                          | <op unit=""></op>   | 1-6  |                                                                                    |                                                     |                                                                             |                    |

| 1.3.  | .4 OP BLOCK Lens composit                           | ison                | 1-7  | 5. AC POWER ADA                                                                    | APTER (AA-V3                                        | 71.1\                                                                       |                    |

| 1.4   | IC BLOCK DIAGRAM                                    |                     | 1-8  |                                                                                    |                                                     |                                                                             | E 1                |

| 1.4.  | .1 IC 1002 (CXD2497R)                               |                     | 1-8  |                                                                                    |                                                     |                                                                             |                    |

|       | .2 IC 2001 (CDS/AGL)                                |                     |      |                                                                                    |                                                     |                                                                             |                    |

|       | .3 IC 7302 (CXA3268AR))                             |                     |      |                                                                                    |                                                     |                                                                             |                    |

|       | .4 LCD (ACX301AK)                                   |                     |      |                                                                                    |                                                     | RD ASSEMBLY <91>                                                            |                    |

| 1.4.  | .5 CCD (ICX262AQ)                                   |                     | 1-12 | MAIN AND T                                                                         | LINIMAL BOA                                         | ND ASSLIVIDLI (812                                                          | 5-5                |

|       | ECTRICAL ADJUSTMENT                                 |                     |      |                                                                                    |                                                     |                                                                             |                    |

| 2.1   | ELECTRICAL ADJUSTMENT                               |                     |      |                                                                                    |                                                     |                                                                             |                    |

| 2.1.  |                                                     |                     |      |                                                                                    |                                                     |                                                                             |                    |

|       | .2 Test instruments required for                    | •                   |      |                                                                                    |                                                     |                                                                             |                    |

|       | .3 Required test equiqment                          |                     |      |                                                                                    |                                                     |                                                                             |                    |

|       | .4 Setup (LCD ADJUSTMENT                            |                     |      |                                                                                    |                                                     |                                                                             |                    |

|       | .5 Setup (CCD ADJUSTMEN)                            |                     |      |                                                                                    |                                                     |                                                                             |                    |

| 2.2   | Setup with patch cords and ji                       | g connector cables  | 2-3  |                                                                                    |                                                     |                                                                             |                    |

|       | HARTS AND DIAGRAMS                                  | 4                   | 0.1  |                                                                                    |                                                     |                                                                             |                    |

|       | ES OF SCHEMATIC DIAGRAN                             |                     |      |                                                                                    |                                                     |                                                                             |                    |

|       | CUIT BOARD NOTES<br>BOARD INTERCONNECTION           |                     |      |                                                                                    |                                                     |                                                                             |                    |

| 3.1   |                                                     |                     |      | SOFTWARE SECTION                                                                   | FOR Windows®                                        | SOFTWARE SECTION I                                                          | FOR Macintosh®     |

| 3.2   | MAIN (SYSCON) SCHEMATIC<br>MAIN (DSP96) SCHEMATIC I |                     |      | <b>Operating Environment</b>                                                       |                                                     | <b>Operating Environment</b>                                                |                    |

| 3.4   | MAIN (DSP97) SCHEMATIC I                            |                     |      | The host computer that runs the                                                    |                                                     | The host computer that runs the                                             |                    |

| 3.5   | MAIN (G/A JCY0148) AND                              | JIAGNAIVI           | 3-9  | operating environment must sa<br>conditions.                                       |                                                     | operating environment must sat<br>conditions.                               | isfy the following |

| 3.5   |                                                     | MATIC DIAGRAM       | 2_11 |                                                                                    |                                                     |                                                                             |                    |

| 3.6   | MAIN (F/Z MDA) AND                                  | IVIATIC DIAGNAMI    | 5-11 | USB Driver 1. Microsoft® Windows® 98/W                                             | indows® 98 Second                                   | USB Driver 1. USB-compatible computer (i                                    | iMac™, iBook™,     |

| 5.0   |                                                     | TIC DIAGRAM         | 2_12 | Edition, pre-installed                                                             | indows 50 Second                                    | Power Mac™ G3/G4, Power                                                     | r Book™ G3, etc.)  |

| 3.7   | MAIN (CDS AGC A/D AND AI                            |                     | 0 12 | <ol> <li>Available USB port</li> <li>CD-ROM drive</li> </ol>                       |                                                     | 2. Mac OS 8.5.1/Mac OS 8.6/N                                                | лас OS 9.0         |

| 5.7   |                                                     | M                   | 3_13 |                                                                                    |                                                     | JVC Video Decoder 1. Power PC 603e/120MHz or                                | factor             |

| 3.8   | MAIN (STROBE CONTROL A                              |                     | 0 10 | Video Player  1. CPU: Intel® Pentium® 200M                                         | Hz class or higher                                  | 2. Mac OS 7.6.1 or later                                                    | iastei             |

| 0.0   |                                                     | M                   | 3-14 | <ol> <li>Microsoft® Windows® 95/W</li> <li>Display capability of 65,536</li> </ol> |                                                     | <ol> <li>QuickTime 3.0 or later</li> <li>Minimum RAM requirement</li> </ol> | · 32MB             |

| 3.9   | CCD SCHEMATIC DIAGRAM                               |                     |      | 4. CD-RÓM drive                                                                    |                                                     | Minimum hard disk space re                                                  |                    |

|       | MONI REG (MONITOR) SCH                              |                     |      | <ol> <li>Minimum RAM requirement</li> <li>Minimum hard disk space re</li> </ol>    | t: 32MB<br>equirement: 1MB                          | * Macintosh® is a registered trac                                           | lemark of Apple    |

|       | MONITOR REG (DC/DC) SCH                             |                     |      | ,                                                                                  | '                                                   | Computer. * Other trademarks are property                                   | of their           |

|       | JACK (VIDEO OUT/USB/PRINTE                          |                     |      | * The system requirements info<br>guarantee that provided softw                    | are applications will                               | owners.                                                                     |                    |

|       |                                                     | SCHEMATIC DIAGRAM . | 3-19 | work on all personal compute<br>requirements.                                      | ers meeting those                                   | * If you use Macintosh® which of port, use an optional flash pat            |                    |

| 3.13  | VOLTAGE CHARTS                                      |                     |      | * Microsoft®, Windows® are eitl                                                    | ner registered                                      | adapter, etc. For details on the                                            | operating en       |

|       | MAIN CIRCUIT BOARD (YB1                             |                     |      | trademarks or trademarks of N<br>in United States and/or other                     |                                                     | ment of these devices, contact<br>manufacturers.                            | tine dealers or    |

|       | MAIN CIRCUIT BOARD (YB1                             |                     |      | * Intel®, Pentium® are registered                                                  |                                                     |                                                                             |                    |

| 3.16  | MONITOR REG CIRCUIT BOX                             | ARD (YB10283-01-02) | 3-35 | corporation.  * Other trademarks are property                                      | of their respective                                 |                                                                             |                    |

|       | MONITOR REG CIRCUIT BOX                             |                     |      | owners.<br>* If you use Windows® 95 or a                                           | •                                                   |                                                                             |                    |

|       | JACK CIRCUIT BOARD (YB10                            |                     |      | which does not have a USB p                                                        | ort, use an optional                                |                                                                             |                    |

|       | JACK CIRCUIT BOARD (YB10                            |                     |      | flash path, conversion card a<br>details on the operating envir                    |                                                     |                                                                             |                    |

|       | CCD CIRCUIT BOARD (YB10                             |                     |      | devices, contact the dealers of                                                    | r manufacturers.                                    |                                                                             |                    |

| 3 21  | CCD CIRCUIT BOARD (VR10                             | 283-01-04)          | 3-11 |                                                                                    |                                                     |                                                                             |                    |

3.22 STOROBE FLASH CIRCUIT BOARD (YB10283-01-02) ...... 3-45 3.23 STOROBE FLASH CIRCUIT BOARD (YB10283-01-04) ...... 3-46 3.25 POWER SUPPLY BLOCK DIAGRAM ...... 3-49 3.26 OP BLOCK SCHEMATIC DIAGRAM <REFERENCE> .. 3-51

SCHEMATIC DIAGRAM <REFERENCE>.......... 3-52

3.27 OPERATION UINT

### **Important Safety Precautions**

Prior to shipment from the factory, JVC products are strictly inspected to conform with the recognized product safety and electrical codes of the countries in which they are to be sold. However, in order to maintain such compliance, it is equally important to implement the following precautions when a set is being serviced.

#### Precautions during Servicing

- Locations requiring special caution are denoted by labels and inscriptions on the cabinet, chassis and certain parts of the product. When performing service, be sure to read and comply with these and other cautionary notices appearing in the operation and service manuals.

- Parts identified by the ▲ symbol and shaded ( ) parts are critical for safety.

Replace only with specified part numbers.

Note: Parts in this category also include those specified to comply with X-ray emission standards for products using cathode ray tubes and those specified for compliance with various regulations regarding spurious radiation emission.

- Fuse replacement caution notice.

Caution for continued protection against fire hazard.

Replace only with same type and rated fuse(s) as specified.

- 4. Use specified internal wiring. Note especially:

- 1) Wires covered with PVC tubing

- 2) Double insulated wires

- 3) High voltage leads

- Use specified insulating materials for hazardous live parts. Note especially:

- 1) Insulation Tape

- 3) Spacers

- 5) Barrier

- 2) PVC tubing

- 4) Insulation sheets for transistors

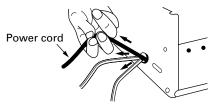

- When replacing AC primary side components (transformers, power cords, noise blocking capacitors, etc.) wrap ends of wires securely about the terminals before soldering.

Fig.1

- 7. Observe that wires do not contact heat producing parts (heatsinks, oxide metal film resistors, fusible resistors, etc.)

- Check that replaced wires do not contact sharp edged or pointed parts.

- 9. When a power cord has been replaced, check that 10-15 kg of force in any direction will not loosen it.

Fig.2

- 10. Also check areas surrounding repaired locations.

- 11. Products using cathode ray tubes (CRTs) In regard to such products, the cathode ray tubes themselves, the high voltage circuits, and related circuits are specified for compliance with recognized codes pertaining to X-ray emission. Consequently, when servicing these products, replace the cathode ray tubes and other parts with only the specified parts. Under no circumstances attempt to modify these circuits. Unauthorized modification can increase the high voltage value and cause X-ray emission from the cathode ray tube.

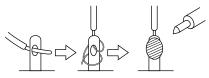

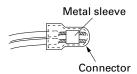

12. Crimp type wire connector

In such cases as when replacing the power transformer in sets where the connections between the power cord and power transformer primary lead wires are performed using crimp type connectors, if replacing the connectors is unavoidable, in order to prevent safety hazards, perform carefully and precisely according to the following steps.

- 1) Connector part number: E03830-001

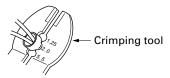

- 2) **Required tool**: Connector crimping tool of the proper type which will not damage insulated parts.

- 3) Replacement procedure

- (1) Remove the old connector by cutting the wires at a point close to the connector.

Important: Do not reuse a connector (discard it).

Fig 3

(2) Strip about 15 mm of the insulation from the ends of the wires. If the wires are stranded, twist the strands to avoid frayed conductors.

Fig.4

(3) Align the lengths of the wires to be connected. Insert the wires fully into the connector.

Fig.5

(4) As shown in Fig.6, use the crimping tool to crimp the metal sleeve at the center position. Be sure to crimp fully to the complete closure of the tool.

ig.6

(5) Check the four points noted in Fig.7.

Not easily pulled free Crimped at approx. center of metal sleeve Conductors extended

Wire insulation recessed more than 4 mm

more than 4 m

Ι

Fig.7

#### Safety Check after Servicing

Examine the area surrounding the repaired location for damage or deterioration. Observe that screws, parts and wires have been returned to original positions, Afterwards, perform the following tests and confirm the specified values in order to verify compliance with safety standards.

#### 1. Insulation resistance test

Confirm the specified insulation resistance or greater between power cord plug prongs and externally exposed parts of the set (RF terminals, antenna terminals, video and audio input and output terminals, microphone jacks, earphone jacks, etc.). See table 1 below.

#### 2. Dielectric strength test

Confirm specified dielectric strength or greater between power cord plug prongs and exposed accessible parts of the set (RF terminals, antenna terminals, video and audio input and output terminals, microphone jacks, earphone jacks, etc.). See table 1 below.

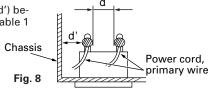

#### 3. Clearance distance

When replacing primary circuit components, confirm specified clearance distance (d), (d') between soldered terminals, and between terminals and surrounding metallic parts. See table 1 below.

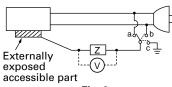

#### 4. Leakage current test

Confirm specified or lower leakage current between earth ground/power cord plug prongs and externally exposed accessible parts (RF terminals, antenna terminals, video and audio input and output terminals, microphone jacks, earphone jacks, etc.).

Measuring Method : (Power ON)

Insert load Z between earth ground/power cord plug prongs and externally exposed accessible parts. Use an AC voltmeter to measure across both terminals of load Z. See figure 9 and following table 2.

Fig. 9

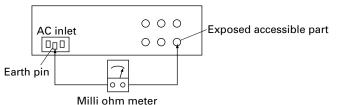

#### 5. Grounding (Class I model only)

Confirm specified or lower grounding impedance between earth pin in AC inlet and externally exposed accessible parts (Video in, Video out, Audio in, Audio out or Fixing screw etc.).

#### Measuring Method:

Connect milli ohm meter between earth pin in AC inlet and exposed accessible parts. See figure 10 and grounding specifications.

Grounding Specifications

| Region             | Grounding Impedance (Z) |

|--------------------|-------------------------|

| USA & Canada       | Z ≦ 0.1 ohm             |

| Europe & Australia | Z ≦ 0.5 ohm             |

| Fi | a | - 1 | 1 |

|----|---|-----|---|

|    |   |     |   |

| AC Line Voltage              | Region             | Insulation Resistance (R)                     | Dielectric Strength                                               | Clearance Distance (d), (d')                                                                       |

|------------------------------|--------------------|-----------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 100 V                        | lanan              | R ≧ 1 MΩ/500 V DC                             | AC 1 kV 1 minute                                                  | d, d' ≧ 3 mm                                                                                       |

| 100 to 240 V                 | Japan              | R ≤ 1 IVI22/500 V DC                          | AC 1.5 kV 1 miute                                                 | d, d' ≧ 4 mm                                                                                       |

| 110 to 130 V                 | USA & Canada       | 1 M $\Omega \le R \le 12$ M $\Omega/500$ V DC | AC 1 kV 1 minute                                                  | d, d' ≧ 3.2 mm                                                                                     |

| 110 to 130 V<br>200 to 240 V | Europe & Australia | R ≧ 10 MΩ/500 V DC                            | AC 3 kV 1 minute<br>(Class II)<br>AC 1.5 kV 1 minute<br>(Class I) | $d \ge 4 \text{ mm}$<br>$d' \ge 8 \text{ mm (Power cord)}$<br>$d' \ge 6 \text{ mm (Primary wire)}$ |

Table 1

Specifications for each region

| AC Line Voltage | Region             | Load Z   | Leakage Current (i)                                    | a, b, c                  |

|-----------------|--------------------|----------|--------------------------------------------------------|--------------------------|

| 100 V           | Japan              | o\/\\\\\ | i ≦ 1 mA rms                                           | Exposed accessible parts |

| 110 to 130 V    | USA & Canada       | 0.15 μF  | i ≦ 0.5 mA rms                                         | Exposed accessible parts |

| 110 to 130 V    | Europe & Australia | o        | $i \le 0.7 \text{ mA peak}$<br>$i \le 2 \text{ mA dc}$ | Antenna earth terminals  |

| 220 to 240 V    | Europe & Australia | ο\\\\\   | i ≦ 0.7 mA peak<br>i ≦ 2 mA dc                         | Other terminals          |

Table 2 Leakage current specifications for each region

Note: These tables are unofficial and for reference only. Be sure to confirm the precise values for your particular country and locality.

## SECTION 1 DISASSEMBLY

#### 1.1 BEFORE ASSEMBLY AND DISASSEMBLY

#### 1.1.1 Precautions

- 1. Be sure to remove the power supply unit prior to mounting and soldering of parts.

- 2. When connecting and disconnecting the connectors, be careful not to damage the wire.

- 3. When replacing chip parts (especially IC parts), desolder completely first (to prevent peeling of the pattern).

- 4. Tighten screws properly during the procedures.

Unless specified otherwise, tighten screws at a torque of 0.1N•m (1.0 kgf•cm).

### CAUTION!! RISK OF ELECTRIC SHOCK

When disassembling the unit, electric hazards may occur in some cases if the capacitor for strobe emission (STROBE board C6512) has been charged. Therefore be also very careful when performing repairs and inspections.

It is recommended that operations be carried out after waiting for more than ten minutes with the power supply removed or after discharging the capacitor forcibly.

Discharge the capacitor according to <NOTE 2> on Page 1-3.

C6512 is located behind the STROBE board.

## PRECAUTIONS ON HANDLING THE LITHIUM SECONDARY BATTERY

This unit is equipped with a coin type lithium secondary battery.

Improper handling of this battery may cause heat to be generated, damage, fires, or leakage. Always follow the precautions below.

- ① Do not short-circuit, disassemble, distort, nor heat the battery.

- 2 Load the battery with its + and poles connected correctly.

- 3 Do not solder the battery itself.

- When replacing parts, also refer to the numbers listed in the Parts List of the manual.

- Do not store the battery in direct sunlight and hot and humid places.

- When replacing the battery, handle it with care and do not attempt to hold it with tweezers as it may short-circuit.

- When disposing the battery, wind tape around the terminal to insulate the battery, and dispose the battery according to the method prescribed.

#### 1.1.2 Assembly and disassembly

| STEP         | PART NAME               | FIG.<br>NO. | POINT                |                                                 | NOTE         |

|--------------|-------------------------|-------------|----------------------|-------------------------------------------------|--------------|

| 1            | FRONT CASE<br>REAR CASE | Fig         |                      | Remove screws<br>2(115), 3(156), 4(114), 1(116) |              |

| 2            | OPERATION UNIT          | 1-2-1       | Remove the Connector | Remove screws<br>3 (116)<br>2 (115)             | NOTE 1       |

| <b>†</b> (1) | (2)                     | (3)         | (4)                  |                                                 | <b>†</b> (5) |

- Indicate the disassembly steps. When assembling, perform in the reverse order of these steps. This number corresponds to the number in the disassembly diagram.

- (2) : Indicates the name of disassembly/assembly parts.

- (3) : Indicates the number in the disassembly diagram.

- (4) : Indicates parts and points such as screws, washers, springs which must be removed during disassembly/ assembly.

Lock (L), soldering (SD), shield, connector, etc.

**Note:** The encircled numbers indicate the order for disassembling the cabinet parts.

The screw numbers indicate the disassembling order.

$\leftrightarrow$ :Wire

⇔:Flat wire

⇒ :Board to Bord Connector

#### [Example]

- (115) = Remove the parts No 115 screw.

- (SD1) = Desoldering at the point SD1.

- (a) = Disconnect the connector/ML (a) .

- (5) : Precautions on disassembly/assembly.

#### 1.1.3 Disconnection of Connectors (Wires)

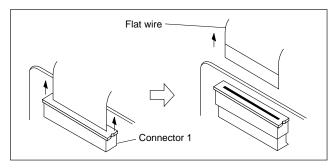

#### Connector

Pull both ends of the connector in the arrow direction, remove the lock and disconnect the flat wire.

Fig. 1-1-1 Connector 1

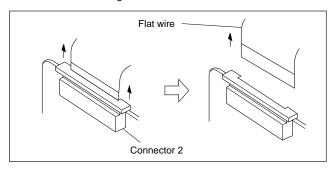

Fig. 1-1-2 Connector 2

Extend the locks in the direction of the arrow for unlocking and then pull out the wire. After removing the wire, immediately restore the locks to their original positions because the locks are apt to come off the connector.

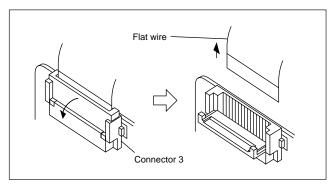

Fig. 1-1-3 Connector 3

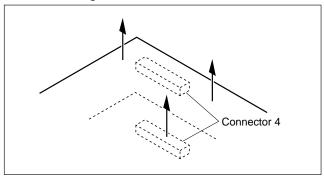

#### B-B connector

Pull the board by both the sides in the direction of the arrow for disconnecting the B-B connector.

Fig. 1-1-4 Connector 4

## 1.2 TOOLS AND EQUIPMENTS REQUIRED FOR ADJUSTMENTS

#### 1.2.1 Tools required for adjustments

#### 1.3 DISASSEMBLY/ASSEMBLY OF CABINET PARTS

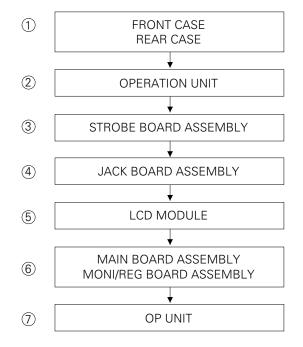

#### 1.3.1 Disassembly flow chart

The following flow chart shows the steps for disassembling the cabinet parts. To assemble, perform the steps of the flow chart in the reverse order.

**Note:** The encircled numbers indicate the order for disassembling the cabinet parts.

The screw numbers indicate the disassembling order.

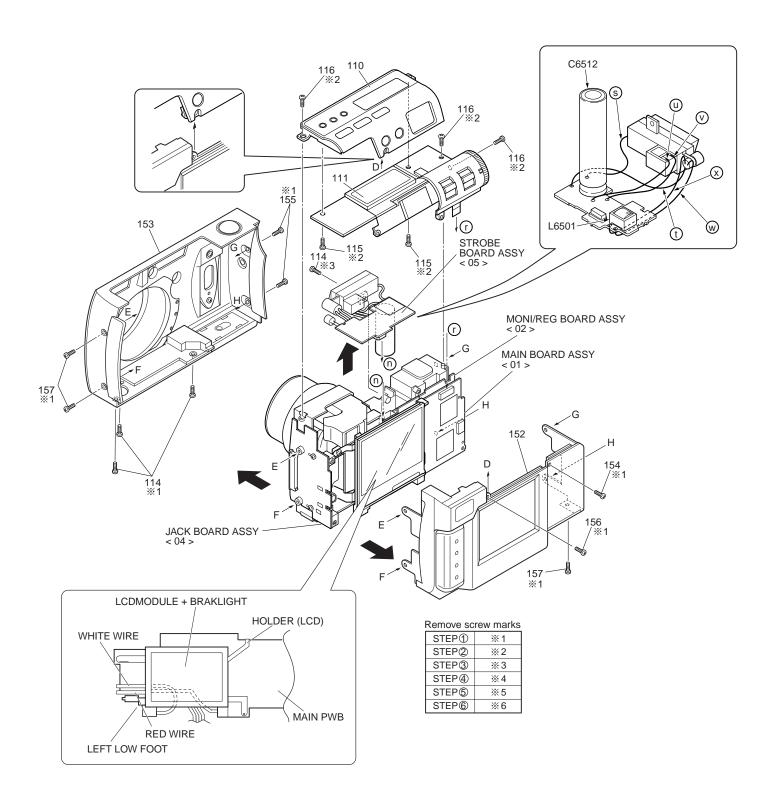

#### 1.3.2 Disassembly method (I)

| STEP | PART NAME                                    | FIG. NO.     | POINT                                                                                                                           |                                                             | NOTE                       |

|------|----------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------|

| 1)   | FRONT CASE<br>REAR CASE                      | Fig          |                                                                                                                                 | Remove screws<br>2 (115), 3 (156), 4 (157), 1 (154)         |                            |

| 2    | OPERATION UNIT                               | 1-3-1        | Remove the Connector  ① MAIN CN4001 ← OPERATION UNIT Remove the TOP COVER                                                       | Remove screws<br>3 (116)<br>2 (115)                         | Note 1                     |

| 3    | STROBE BOARD ASSEMBLY                        | Fig<br>1-3-1 | Remove the Connector                                                                                                            | Remove screw<br>1 (114)                                     | Note 1<br>Note 2           |

|      | JACK BOARD ASSEMBLY                          |              | Remove the Connector  ② MAIN CN5501 ← JACK CN101  ③ LCD MODULE (BL) ← JACK CN701                                                | Remove screws<br>2 (114)<br>(e) (SD3), (f) (SD4), (g) (SD5) |                            |

| 4    | LCD MODULE                                   | Fig          | Remove the Connector  ♠ MAIN CN3002 ← LCD MODULE (LCD)  Remove from the Frame Assy  Remove from the LCD Holder                  | Remove screws<br>2 (114)                                    | Note 1<br>Note 3<br>Note 4 |

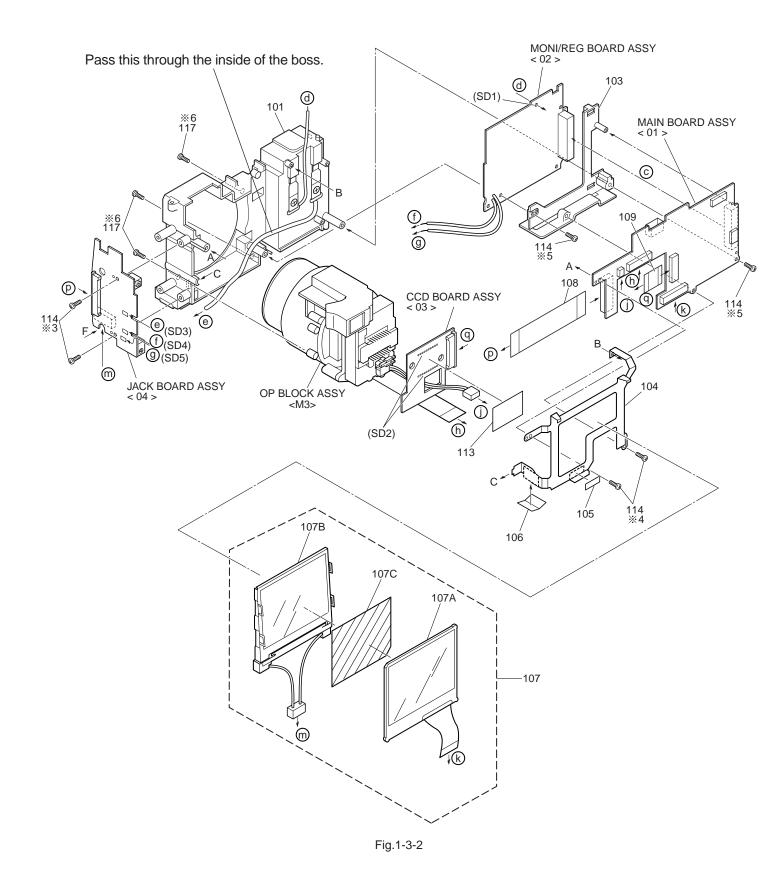

| (5)  | MAIN BOARD ASSEMBLY  MONI/REG BOARD ASSEMBLY | 1-3-2        | Remove the Connector  ① MAIN CN501 ← OP UNIT ② MAIN CN3001 ← MON/REG CN9001 ③ MON/REG TL9001 ← Frame Assy Remove the PWB HOLDER | ①(SD1)<br>Remove screws 2 (114)                             | Note 1                     |

| 6    | OP UNIT                                      | Fig<br>1-3-3 | Remove from the Frame Assy                                                                                                      | Remove screws 3 (117)                                       |                            |

| CONNEC-<br>TOR/HL | NO.OF<br>PINS | CON                                 | NECTION                                                           |

|-------------------|---------------|-------------------------------------|-------------------------------------------------------------------|

| C                 | 80            | MAIN Board CN3001                   | ← MONI/REG Board CN9001                                           |

| (d)               | 1             | MONI/REG Board TL9001               | $\longleftrightarrow$ main frame (RED)                            |

| e                 | 1             | JACK Board TP3                      | ←→ MAIN FRAME (BROWN)                                             |

| f                 | 1             | JACK Board TP2                      | ←→ MONI/REG Board J9001 (BLACK)                                   |

| 9                 | 1             | JACK Board TP1                      | ←→ MONI/REG Board J9002 (RED)                                     |

| h                 | 22            | MAIN Board CN501                    | ⇔ OP UNIT                                                         |

| <u> </u>          | 2             | MAIN Board CN502                    | <→ OP UNIT                                                        |

| k                 | 24            | MAIN Board CN3002                   | $\iff$ LCD MODULE (LCD)                                           |

| m                 | 2             | JACK Board CN701                    | ⇔ LCD MODULE (BL)                                                 |

| n                 | 14            | MAIN Board CN6601                   | ← STROBE Board CN6501                                             |

| (P)               | 38            | MAIN Board CN5501                   | ⇔ JACK Board CN101                                                |

| (P)               | 28            | MAIN Board CN2001                   | ← CCD Board CN1001                                                |

| (1)               | 12            | MAIN Board CN4001                   | ⇔ OPERATION UNIT                                                  |

| S                 | 1             | STROBE UNIT WIRE (ORANGE)           | $\longleftrightarrow {\tt STROBE\ Board\ J6501\ (Through\ hole)}$ |

| t                 | 1             | STROBE UNIT WIRE (BROWN)            | $\longleftrightarrow$ STROBE Board J6502 (Through hole)           |

| Ü                 | 1             | STROBE UNIT WIRE (RED)              | $\longleftrightarrow$ STROBE Board J6503 (Through hole)           |

| V                 | 1             | STROBE UNIT WIRE (BLACK)            | $\longleftrightarrow$ STROBE Board J6504 (Through hole)           |

| w                 | 1             | STROBE UNIT WIRE (Red, Thin wire)   | ← STROBE Board J6505 (Through hole)                               |

| X                 | 1             | STROBE UNIT WIRE (BLACK, Thin wire) | ←→ STROBE Board J6506 (Through hole)                              |

#### Note 1

Destination of connectors.

**Note:** Three kinds of double-arrows in connection tables respectively show kinds of connector/wires.

→ : Board to Board connector

$\iff : \textit{ Flat wire } \\ \iff : \textit{ Wire }$

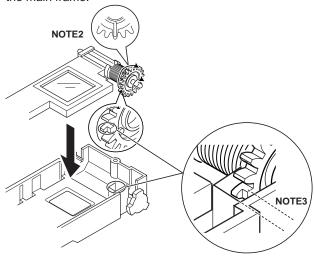

#### Note 2

Be careful from electric shock hazard because the capacitor (C6512) for the strobe is exposed. Be sure to positively discharge the capacitor if it is energized by short-circuiting a resistor (10 - 22 k) connected at both capacitor terminals. Please be very careful when doing this job.

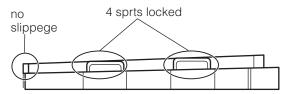

#### Note 3

Make sure that there is no slippage between the LCD panel and the backlight, the four spots are locked with hooks securely, and the sheet is placed in the correct direction.

#### Note 4

Both the stripe pattern and the non-slippage (notch) on the sheet surface are to be in the direction as illustrated.

Fig.1-3-1

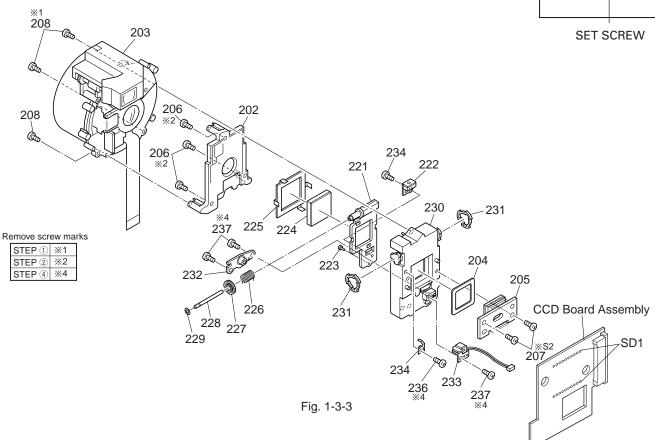

#### 1.3.3 Disassembly method (II) <OP Unit>

| STEP | PART NAME         | POINT                          | NOTE   |

|------|-------------------|--------------------------------|--------|

| 1    | OP Block ASSEMBLY | Remove screws 3 (208)          |        |

| 2    | COVER             | Remove screws 3 (206),2 (207), |        |

|      | CCD BASE ASSEMBLY | 1 (236)                        |        |

|      | SPACER            | Remove screws 3(206),2(207).   |        |

|      | SET PLATE         | Remove the CCD Board Assy      |        |

|      |                   | 20(SD1)                        |        |

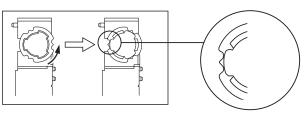

| 3    | TILT FRAME        | Remove the SET RING            | Note 1 |

|      | RATCH GEAR        | 2 (231)                        | Note 2 |

|      | MAIN PIN          |                                | Note 3 |

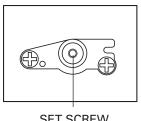

| 4    | RATCH MAGNET      | Remove Screws                  | Note 4 |

|      | NUT ASSEMBLY      | 3 (237),1 (236)                |        |

|      | RATCH PIECE       |                                |        |

Note 1 Turn and fix the set ring and make sure that the convex marks are identical.

#### Note 2

Make sure that the torsion spring is in the groove of the latch gear.

#### Note 3

Turn the latch gear clockwise (( ) and position it so that the toothless portion comes to the level that is as high as the main frame.

**Note 4**Never move the setscrew in the center of the nut assembly!

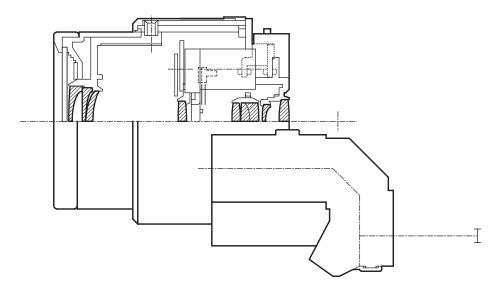

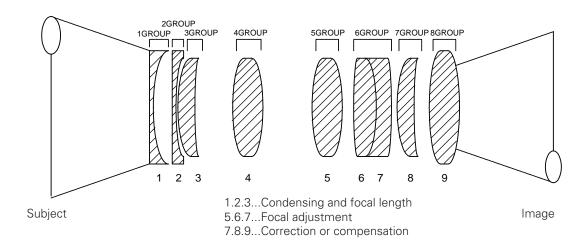

#### 1.3.4 OP BLOK Lens Compositison

Fig. 1-3-4 Composition of GC-QX3U Lens (8-group 9-element lens composition)

Fig. 1-3-5 8-group-9-piece lens composition

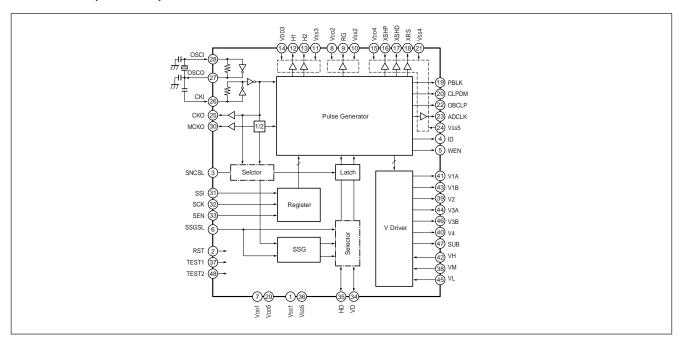

#### 1.4 IC BLOCK DIAGRAM

#### 1.4.1 IC 1002 (CXD2497R)

#### **Pin Descriptions**

| Pin No. | Pin Name          | 1/0 | Description                                                                             |  |

|---------|-------------------|-----|-----------------------------------------------------------------------------------------|--|

| 1       | Vss1              | -   | GND                                                                                     |  |

| 2       | RST               | Ι   | System reset input terminal H: Reset released L: Reset activated                        |  |

|         |                   |     | (Should be activated at power ON, normally.)                                            |  |

|         |                   |     | (Schmitt trigger input/without protection diode on power supply side)                   |  |

| 3       | SNCSL             | Τ   | Sync system switching control input terminal                                            |  |

|         |                   |     | (with pull-down resistor)                                                               |  |

|         |                   |     | H: CKI sync L: MCKO sync                                                                |  |

| 4       | ID                | 0   | Line identification pulse output terminal in the vertical direction                     |  |

| 5       | WEN               | 0   | Memory write timing pulse output terminal                                               |  |

| 6       | SSGSL             | Ι   | Built-in SSG enable input terminal (with pull-down resistor)                            |  |

|         |                   |     | H: Built-in SSG is effective. L: External sync is effective.                            |  |

| 7       | VDD1              | -   | 3.3V power (for common logic section)                                                   |  |

| 8       | V <sub>DD</sub> 2 | -   | 3.3V power (for RG terminal)                                                            |  |

| 9       | RG                | 0   | Reset gate pulse output terminal for CCD                                                |  |

| 10      | Vss2              | -   | GND                                                                                     |  |

| 11      | Vss3              | -   | GND                                                                                     |  |

| 12      | H1                | 0   | Clock output terminal for CCD horizontal register                                       |  |

| 13      | H2                | 0   | Clock output terminal for CCD horizontal register                                       |  |

| 14      | VDD3              | -   | 3.3V to 5.0V power (for H1 and H2 terminals)                                            |  |

| 15      | VDD4              | -   | 3.3V power (for CDS system terminals)                                                   |  |

| 16      | XSHP              | 0   | CCD pre-charge level sample/hold pulse output terminal                                  |  |

| 17      | XSHD              | 0   | CCD data level sample/hold pulse output terminal                                        |  |

| 18      | XRS               | 0   | Sample/hold pulse output terminal for phase matching in analog-to-digital conversion    |  |

| 19      | PBLK              | 0   | Pulse output terminal for pulse cleaning during horizontal and vertical blanking period |  |

| 20      | CLPDM             | 0   | Pulse output terminal for CCD dummy signal clamping                                     |  |

| 21      | Vss4              | -   | GND                                                                                     |  |

| 22      | OBCLP             | 0   | Pulse output terminal for CCD optical black signal                                      |  |

| 23      | ADCLK             | 0   | Clock output terminal for analog-to-digital conversion IC                               |  |

|         |                   |     | Logical phase is adjustable with the serial interface data                              |  |

| 24 | Vss5  | _   | GND                                                                                                                                   |  |

|----|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------|--|

| 25 | CKO   | 0   | Inverter output terminal                                                                                                              |  |

| 26 | CKI   | T T | Inverter input terminal                                                                                                               |  |

| 27 | OSCO  | 0   | Inverter output terminal for oscillation (If not used, should be opened or connected to GND through a capacitor.)                     |  |

| 28 | OSCI  | I   | Inverter input terminal for oscillation (If not used, should be fixed to "Low".)                                                      |  |

| 29 | VDD5  | -   | 3.3V power (for common logic section)                                                                                                 |  |

| 30 | MCKO  | 0   | System clock output terminal for signal processing IC                                                                                 |  |

| 31 | SSI   | I   | Serial interface data input terminal for setting each IC mode (Schmitt trigger input/without protection diode on power supply side)   |  |

| 32 | SCK   | I   | Serial interface clock input terminal for setting each IC mode (Schmitt trigger input/without protection diode on power supply side)  |  |

| 33 | SEN   | I   | Serial interface strobe input terminal for setting each IC mode (Schmitt trigger input/without protection diode on power supply side) |  |

| 34 | VD    | 1/0 | Vertical sync signal input/output terminal                                                                                            |  |

| 35 | HD    | 1/0 | Horizontal sync signal input/output terminal                                                                                          |  |

| 36 | Vss6  | -   | GND                                                                                                                                   |  |

| 37 | TEST1 | I   | IC test terminal 1 with pull-down resistor (Should be fixed to GND normally.)                                                         |  |

| 38 | VM    | -   | GND (for vertical drivers)                                                                                                            |  |

| 39 | V2    | 0   | Clock output terminal for CCD vertical register                                                                                       |  |

| 40 | V4    | 0   | Clock output terminal for CCD vertical register                                                                                       |  |

| 41 | V1A   | 0   | Clock output terminal for CCD vertical register                                                                                       |  |

| 42 | VH    | -   | 15.0V power (for vertical drivers)                                                                                                    |  |

| 43 | V1B   | 0   | Clock output terminal for CCD vertical register                                                                                       |  |

| 44 | V3A   | 0   | Clock output terminal for CCD vertical register                                                                                       |  |

| 45 | VL    | -   | -7.5V power (for vertical drivers)                                                                                                    |  |

| 46 | V3B   | 0   | Clock output terminal for CCD vertical register                                                                                       |  |

| 47 | SUB   | 0   | Pulse output terminal for CCD electronic shutter                                                                                      |  |

| 48 | TEST2 | I   | IC test terminal 2 with pull-down resistor (Should be fixed to GND normally.)                                                         |  |

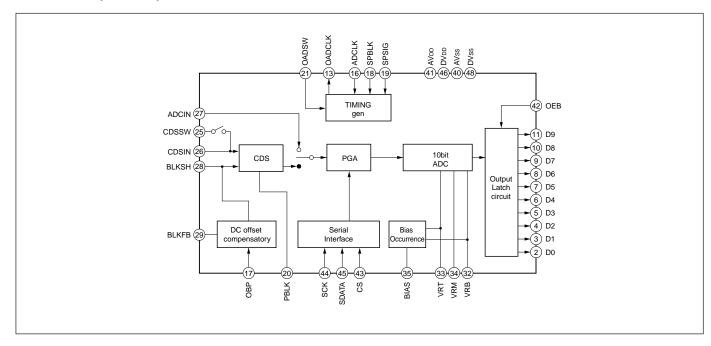

#### 1.4.2 IC 2001 (CDS/AGL)

#### **Pin Descriptions**

| Pin No. | Pin Name                  | Description                                       |   | Analog (A) or<br>Digital (D) |

|---------|---------------------------|---------------------------------------------------|---|------------------------------|

| 1       | NC No internal connection |                                                   | - | -                            |

| 2       | D0                        | Digital output terminal (LSB)                     | 0 | D                            |

| 3-10    | D1-D8                     | Digital output terminals                          | 0 | D                            |

| 11      | D9                        | Digital output terminal (MSB)                     | 0 | D                            |

| 12      | NC                        | No internal connection                            | - | -                            |

| 13      | OADCLK                    | Latch clock output terminal for D0 to D9          | 0 | D                            |

| 14      | DVss                      | Digital GND (0V)                                  | - | D                            |

| 15      | DVDD                      | Power for digital 3.0V system                     | - | D                            |

|         |                           | (Should be connected to AVDD outside the IC.)     |   |                              |

| 16      | ADCLK                     | Analog-to-digital conversion clock input terminal | - | D                            |

| 17      | OBP                       | Optical black pulse input terminal                | - | D                            |

| 18      | SPBLK                     | Black level sampling clock input terminal         | - | D                            |

| 19      | SPSIG                     | Signal level sampling clock input terminal        | - | D                            |

| 20      | PBLK                      | PBLK Pre-blanking signal input terminal           |   | D                            |

| 21      | OADSW                     | ADSW OADCLK enable input terminal                 |   | D                            |

| 22      | AVss                      | Analog GND (0V)                                   |   | Α                            |

| 23      | AVDD                      | Power for analog 3.0V system                      |   | Α                            |

| 24      | NC                        | No internal connection                            |   | -                            |

| 25      | CDSSW                     | Signal level sampling output terminal             | 0 | Α                            |

| 26      | CDSIN                     | CDS input terminal                                |   | Α                            |

| 27      | ADCIN                     | ADC input terminal                                | - | Α                            |

| 28      | BLKSH                     | Black level sample/hold terminal                  | - | Α                            |

| 29      | BLKFB                     | Black level feedback terminal                     | - | Α                            |

| 30      | AVss                      | Analog GND (0V)                                   | - | Α                            |

| 31      | AVDD                      | Power for analog 3.0V system                      | - | Α                            |

|         |                           | (Should be connected to DVDD outside the IC.)     |   |                              |

| 32      | VRT                       | Reference voltage terminal 3                      | - | Α                            |

|         |                           | (Ceramic capacitor of 0.1µF or more should be     |   |                              |

|         |                           | connected between this terminal and AVss.)        |   |                              |

| 33      | VRB                       | Reference voltage terminal 2                      | - | А                            |

|         |                           | (Ceramic capacitor of 0.1µF or more should be     |   |                              |

|         |                           | connected between this terminal and AVss.)        |   |                              |

| 34    | VRM              | Reference voltage terminal 1                  |   | Α |

|-------|------------------|-----------------------------------------------|---|---|

|       |                  | (Ceramic capacitor of 0.1µF or more should    |   |   |

|       |                  | be connected between this terminal and AVss.) |   |   |

| 35    | BIAS             | Internal bias terminal                        | - | А |

|       |                  | (A 24-Kohm resistor should be connected       |   |   |

|       |                  | between this terminal and AVss.)              |   |   |

| 36    | NC               | No internal connection                        | - | - |

| 37    | AVss             | Analog GND (0V)                               | - | А |

| 38    | AVdd             | Power for analog 3.0V system                  | - | А |

|       |                  | (Should be connected to DVpp outside the IC.) |   |   |

| 39    | NC               | No internal connection                        | - | - |

| 40    | AVss             | Analog GND (0V)                               | - | А |

| 41    | AVdd             | Power for analog 3.0V system                  | - | А |

|       |                  | (Should be connected to DVpp outside the IC.) |   |   |

| 42    | OEB              | Digital output enable control input terminal  | Π | D |

| 43    | CS               | Serial interface control input terminal       | Π | D |

| 44    | SCK              | Serial clock input terminal                   | П | D |

| 45    | SDATA            | Serial data input terminal                    |   | D |

| 46    | DV <sub>DD</sub> | Power for digital 3.0V system                 | - | D |

|       |                  | (Should be connected to AVDD outside the IC.) |   |   |

| 47,48 | DVss             | Digital GND                                   | - | D |

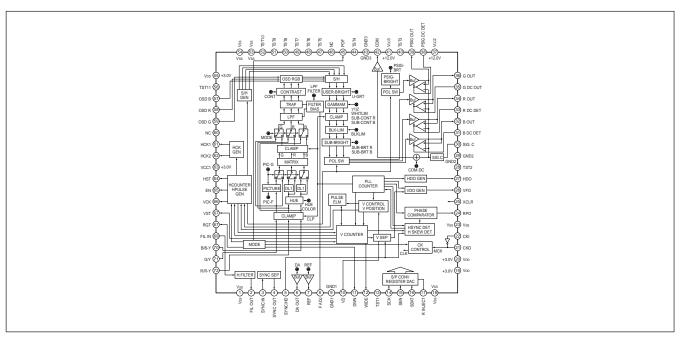

#### 1.4.3 IC 7302 (CXA3268AR)

#### **Pin Descriptions**

| Pin No. | Pin Name | 1/0 | Description                                                                       | Input<br>Res. |

|---------|----------|-----|-----------------------------------------------------------------------------------|---------------|

| 1       | Vss      | -   | GND terminal for digital 3.0V system                                              |               |

| 2       | FIL OUT  | 0   | H filter output terminal (for internal sync separator use)                        |               |

| 3       | SYNC IN  | I   | Sync input terminal for sync separator circuit (for internal sync separator use)  |               |

| 4       | SYNC OUT | 0   | Sync output terminal for sync separator circuit (for internal sync separator use) |               |

| 5       | CSYNC/HD | Ι   | CSYNC/horizontal sync signal input terminal                                       |               |

| 6       | DA OUT   | 0   | DAC output terminal                                                               |               |

| 7       | REF      | 0   | Level shifter circuit reference voltage output terminal for LCD panel             |               |

| 8       | F ADJ    | 0   | fO adjust resistor connecting terminal for TRAP                                   |               |

| 9       | GND1     | -   | GND terminal for analog 3.0V system                                               |               |

| 10      | VD       | Ι   | Vertical sync signal input terminal                                               | L             |

| 11      | DWN      | 0   | Up/Down switching signal output terminal                                          |               |

| 12      | WIDE     | 0   | 16:9 wide display switching pulse output terminal                                 |               |

| 13      | TST1     | -   | Test terminal (Should be opened.)                                                 |               |

| 14      | SCK      | Ι   | Serial clock input terminal                                                       |               |

| 15      | SEN      | Ι   | Serial load input terminal                                                        |               |

| 16      | SDAT     | Ι   | Serial data input terminal                                                        |               |

| 17      | R INJECT | 0   | Resistor connecting terminal for serial block current control                     |               |

| 18      | Vss      | -   | GND terminal for digital 3.0V system                                              |               |

| 19      | VDD      | -   | Power for digital 3.0V system                                                     |               |

| 20      | Vdd      | -   | Power for digital 3.0V system                                                     |               |

| 21      | CKO      | 0   | Oscillation cell output terminal                                                  |               |

| 22      | CKI      | Ι   | Oscillation cell input terminal                                                   |               |

| 23      | Vss      | -   | GND terminal for digital 3.0V system                                              |               |

| 24      | RPD      | 0   | Phase comparison output terminal                                                  |               |

| 25      | XCLR     | I   | Capacitor connecting terminal for power-on reset (for timing generating system)   | Н             |

| 26      | VD0      | 0   | VDO pulse output terminal                                                         |               |

| 27      | HD0      | 0   | HDO pulse output terminal                                                         |               |

| 28      | TST2     | -   | Test terminal (Should be connected to GND.)                                       |               |

| 29      | GND2     | -   | GND terminal for analog 12.0V system                                              |               |

| 30      | SIG.C    | Ι   | DC voltage adjust terminal for R, G, B and PSIG outputs                           |               |

| 31      | B DC DET | 0   | Capacitor connecting terminal for B signal's DC voltage feedback circuit          |               |

| 32      | B OUT    | 0   | B signal output terminal                                                          |               |

| 33      | R DC DET | 0   | Capacitor connecting terminal for R signal's DC voltage feedback circuit          |               |

| 34      | R OUT    | 0   | R signal output terminal                                                          |               |

| 35      | G DC DET | 0   | Capacitor connecting terminal for G signal's DC voltage feedback circuit          |               |

| 1  |          |   |                                                             |  |

|----|----------|---|-------------------------------------------------------------|--|

| 36 | G OUT    | 0 | G signal output terminal                                    |  |

| 37 | Vcc2     | - | Power for analog 12.0V system                               |  |

| 38 | PSIG DC  | 0 | Capacitor connecting terminal for G signal's DC voltage     |  |

|    | DET      |   | feedback circuit                                            |  |

| 39 | PSIG OUT | 0 | PSIG output terminal                                        |  |

| 40 | TST3     | - | Test terminal (Should be opened.)                           |  |

| 41 | Vcc3     | - | Power for analog 12.0V system COM (CS)                      |  |

| 42 | COM      | 0 | Common electrode voltage output terminal (CS) for LCD panel |  |

| 43 | GND3     | - | GND terminal for analog 12.0V system COM (CS)               |  |

| 44 | TST4     | - | Test terminal (Should be opened.)                           |  |

| 45 | P0F      | 0 | LCD panel power ON/OFF terminal                             |  |

|    |          |   | (Open, if this function is not used.)                       |  |

| 46 | NC       | - | No internal connection                                      |  |

| 47 | TST5     | - | Test terminal (Should be connected to GND.)                 |  |

| 48 | TST6     | - | Test terminal (Should be connected to GND.)                 |  |

| 49 | TST7     | - | Test terminal (Should be opened.)                           |  |

| 50 | TST8     | - | Test terminal (Should be opened.)                           |  |

| 51 | TST9     | - | Test terminal (Should be opened.)                           |  |

| 52 | TST10    | - | Test terminal (Should be opened.)                           |  |

| 53 | Vss      | - | GND terminal for digital 3.0V system                        |  |

| 54 | Vss      | - | GND terminal for digital 3.0V system                        |  |

| 55 | VDD      | - | Power for digital 3.0V system                               |  |

| 56 | TST11    | - | Test terminal (Should be connected to GND.)                 |  |

| 57 | OSD B    | Ι | OSD B input terminal                                        |  |

| 58 | OSD R    | Ι | OSD R input terminal                                        |  |

| 59 | OSD G    | Ι | OSD G input terminal                                        |  |

| 60 | NC       | - | No internal connection                                      |  |

| 61 | HCK1     | 0 | H clock pulse 1 output terminal                             |  |

| 62 | HCK2     | 0 | H clock pulse 2 output terminal                             |  |

| 63 | Vcc1     | - | Power for analog 3.0V system                                |  |

| 64 | HST      | 0 | H start pulse output terminal                               |  |

| 65 | EN       | 0 | EN pulse output terminal                                    |  |

| 66 | VCK      | 0 | V clock pulse output terminal                               |  |

| 67 | VST      | 0 | V start pulse output terminal                               |  |

| 68 | RGT      | 0 | Right/Left switching signal output terminal                 |  |

| 69 | FIL IN   | Ι | H FILTER input terminal (for internal sync separator use)   |  |

| 70 | B/B-Y    | Τ | B/B-Y signal input terminal                                 |  |

| 71 | G/Y      | Т | G/Y signal input terminal                                   |  |

| 72 | R/R-Y    | Ι | R/R-Y signal input terminal                                 |  |

<sup>\*</sup> DWN: <u>DOWN</u> SCAN and UP SCAN H: Pull-up resistor incorporated

RGT: <u>RIGHT</u> SCAN and LEFT SCAN L: Pull-down resistor incorporated

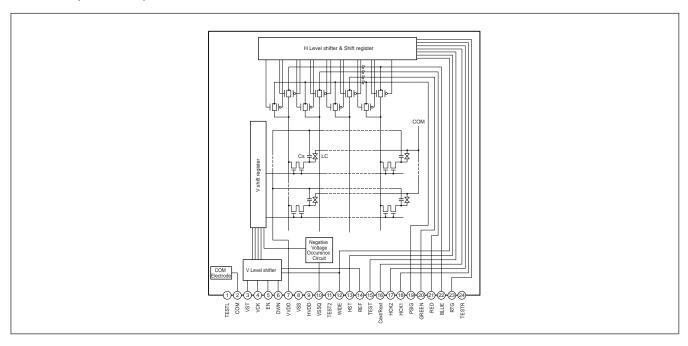

#### 1.4.4 LCD (ACX301AK)

#### **Pin Descriptions**

| Pin No. | Pin Name  | Description                                                           |

|---------|-----------|-----------------------------------------------------------------------|

| 1       | TESTL     | Panel testing terminal (Should be opened.)                            |

| 2       | COM       | Common electrode voltage input terminal for panel                     |

| 3       | VST       | Start pulse input terminal for V shift register drive                 |

| 4       | VCK       | Clock input terminal for V shift register drive                       |

| 5       | EN        | Enable signal input terminal for gate select pulse                    |

| 6       | DWN       | Drive direction signal input terminal for V shift register            |

| 7       | VVDD      | Power for V driver                                                    |

| 8       | Vss       | GND for H and V drivers                                               |

| 9       | HVdd      | Power for H driver                                                    |

| 10      | VSSG      | Negative voltage setting terminal for V driver                        |

| 11      | TEST2     | Connected to GND through a 1-Mohm resistor in the panel               |

| 12      | WIDE      | Pulse input terminal for 16:9 mode                                    |

| 13      | HST       | Start pulse input terminal for H shift register drive                 |

| 14      | REF       | Level shifter circuit reference voltage input terminal                |

| 15      | TEST      | Panel testing terminal (Should be opened.)                            |

| 16      | Cext/Rext | Power input terminal for setting H shift register drive time constant |

| 17      | HCK2      | Clock input terminal for H shift register drive                       |

| 18      | HCK1      | Clock input terminal for H shift register drive                       |

| 19      | PSIG      | Uniformity improving signal input terminal                            |

| 20      | GREEN     | Video signal (G) input terminal for the panel                         |

| 21      | RED       | Video signal (R) input terminal for the panel                         |

| 22      | BLUE      | Video signal (B) input terminal for the panel                         |

| 23      | RGT       | Drive direction signal input terminal for H shift register            |

| 24      | TESTR     | Panel testing terminal (Should be opened.)                            |

#### **Features**

- Device Structure

- Active matrix panel with internal driver using low-temperature polysilicon transistors

- Pixels

Total dots: 896 (H) x 230 (V) =206,080 Display dots: 880 (H) x 228 (V) =200,640 (2.0 in.)

- Total dots: 200,000 dots 5.1cm diagonal (2.0 in.)

- Horizontal resolution: 440 TV scanning lines

- Light permeability: 5.6% (standard)

- Smooth screen image with RGB delta array

- NTSC/PAL compatible

- High image quality internal circuitry

- 16:9 screen display function

- Low-reflection screen display processing assures easy viewing even outdoors

- Anti-grime display

Delta array

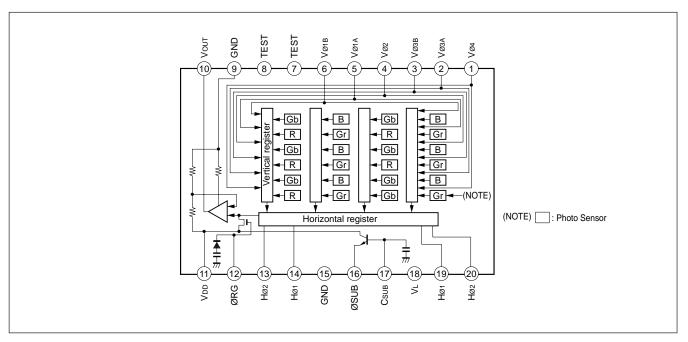

#### 1.4.5 CCD (ICX262AQ)

#### **Pin Descriptions**

| Pin No. | Pin Name | Description                        |

|---------|----------|------------------------------------|

| 1       | Vø4      | Vertical register transfer clock   |

| 2       | Vø3A     | Vertical register transfer clock   |

| 3       | Vø3B     | Vertical register transfer clock   |

| 4       | Vø2      | Vertical register transfer clock   |

| 5       | Vø1A     | Vertical register transfer clock   |

| 6       | Vø3B     | Vertical register transfer clock   |

| 7       | TEST     | Test terminal*1                    |

| 8       | TEST     | Test terminal*1                    |

| 9       | GND      | GND                                |

| 10      | Vout     | Signal output                      |

| 11      | Vdd      | Circuit power                      |

| 12      | øRG      | Reset gate clock                   |

| 13      | Hø2      | Horizontal register transfer clock |

| 14      | Hø1      | Horizontal register transfer clock |

| 15      | GND      | GND                                |

| 16      | øSUB     | PCB clock                          |

| 17      | Csub     | PCB bias*2                         |

| 18      | VL       | Protection transistor bias         |

| 19      | Hø1      | Horizontal register transfer clock |

| 20      | Vø2      | Horizontal register transfer clock |

- \*1: Terminal should be opened.

- \*2: A  $0.1\mu F$  capacitor should be connected between the pin and GND, since the DC bias is generated inside the CCD.

#### **Features**

- Field period readout system

- Interline CCD image sensor

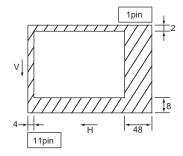

- Total number of pixels: 2140 (H) x 1560 (V) approx. 3340k pixels

- Number of effective pixels: 2088 (H) x 1550 (V) approx. 3240k pixels

- Effective number of pixels: 2080 (H) x 1542 (V) approx. 3210k pixels (1.18in)

- Chip size: 8.10mm (H) x 6.64mm (V)

- Unit cell size: 3.45m m (H) x 3.45m m (V)

- Optical black:

Horizontal (H) direction: front 4 pixels, rear 48 pixels Vertical (V) direction: front 8 pixels, rear 2 pixels

- Number of dummy bits: Horizontal 28 Vertical 1 (even fields only)

- Square pixels

- Horizontal drive frequency: 18kHz

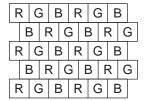

- RGB basic color mosaic on-chip color filter

- High sensitivity

- Cyclic, variable speed shutter

- Excellent anti-blooming characteristics

Optical black wiring diagram (Top View)

## SECTION 2 ELECTRICAL ADJUSTMENT

#### 2.1 ELECTRICAL ADJUSTMENT

#### 2.1.1 Precautions

Both the camera section and deck section of this model are designed and manufactured to be adjustment-free. However, if both or either of the following parts is replaced, it needs special adjustment with a personal computer at a JVC service equipment after the part replacement

- OP block assembly

- EEPROM (on the MAIN board)

When there is some trouble in the electric circuit, it is required to detect the faulty part with specified test instruments first and then to proceed to repair, replacement and adjustment.

- When cheking a signal at a chip test point, be sure to use an IC clip or the like not to apply any stress to the test point. When replacing a chip part (IC in particular), completely remove solder chips from it and its periphery before proceeding to part replacement (in order to avoid exfoliation of the pattern).

- Carefully disconnect/connect connectors because they are apt to get damaged.

### 2.1.2 Test instruments required for electrical adjustment

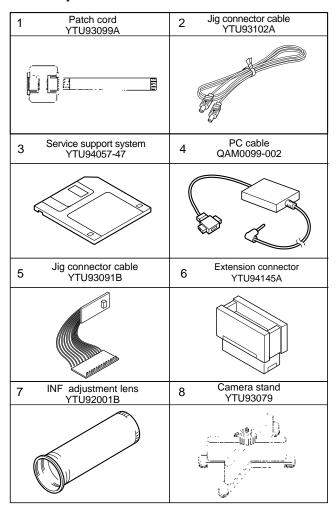

#### 2.1.3 Required test equipment

- 1. Color TV monitor.

- 2. AC power adapter (AA-V37 or equivalent)

- 3. Oscilloscope (dual-trace type, for more than 20 MHz).

- 4. Digital voltmeter

- 5. Frequency counter (with threshold level adjuster)

- 6. Personal computer

#### 2.1.4 Setup (LCD ADJUSTMENT)

Setup for electrical adjustment with personal computer

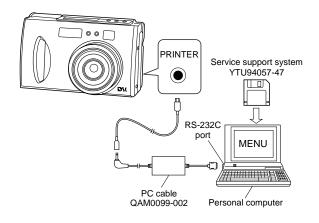

**Note 1:** As a general rule for adjustment with a personal computer, connect a personal computer to its PRINTER terminal.

Note 2: Use DC cord to supply the power.

Fig. 2-1-1 Setup for electrical adjustment with personal computer (I)

Fig. 2-1-2 Setup for electrical adjustment with personal computer (II)

| Pin No. | FUNCTION  |  |  |  |

|---------|-----------|--|--|--|

|         |           |  |  |  |

| 1       | 135TMS    |  |  |  |

| 2       | 135TDI    |  |  |  |

| 3       | nTRST     |  |  |  |

| 4       | AL_3.3V   |  |  |  |

| 5       | 32DBI     |  |  |  |

| 6       | GND       |  |  |  |

| 7       | M_COM     |  |  |  |

| 8       | M_SIG_C   |  |  |  |

| 9       | M_RED     |  |  |  |

| 10      | M_SIG_GND |  |  |  |

| 11      | JTAGMODE  |  |  |  |

| 12      | 135TD0    |  |  |  |

| 13      | 135TCK    |  |  |  |

| 14      | AL_3.3V   |  |  |  |

| 15      | 32RST     |  |  |  |

| 16      | M_BLUE    |  |  |  |

| 17      | RPD       |  |  |  |

| 18      | M_PSIG    |  |  |  |

| 19      | M_GREEN   |  |  |  |

| 20      | NC        |  |  |  |

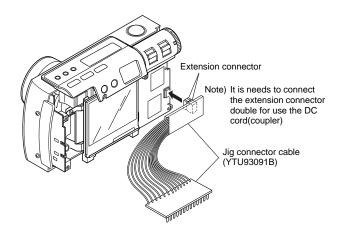

Table 2-1-1 Jig Connector Function

#### 2.1.5 Setup (CCD ADJUSTMENT)

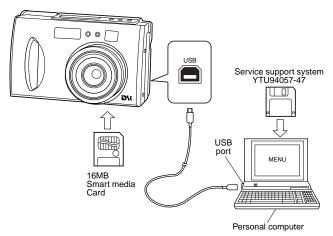

Setup for electrical adjustment with personal computer

**Note 1:** As a general rule for adjustment with a personal computer, connect a personal computer to its DIGITAL terminal.

Note 2: Use DC cord to supply the power.

Fig. 2-1-3 Setup for electrical adjustment with personal computer (I)

#### 2.2 Setup with patch cords and jig connector cables

#### Note:

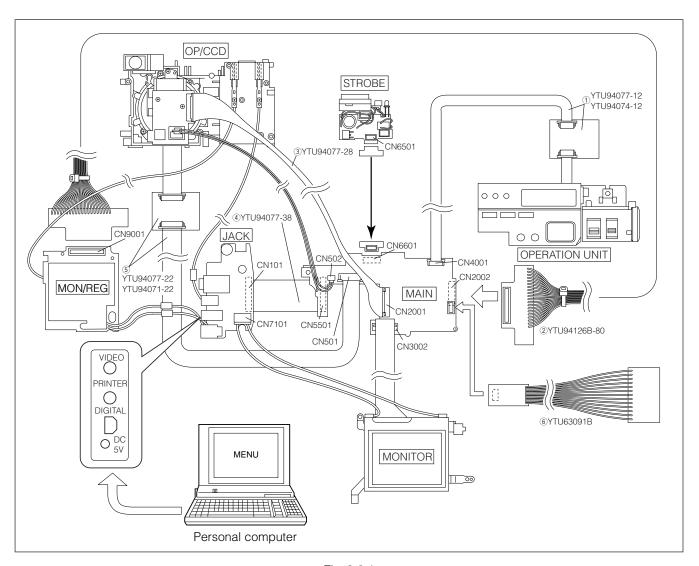

Fig. 2-2-1 shows an example of expansion setup that facilitates inspection of major boards because main components are connected by means of patch cords and jir cables. For proceeding to electrical adjustment in such the setup, disassemble the set at certain level required for the current adjustment objectives referring to the section 1 "DISASSEMBLY" and properly set up the expanded set and test instruments.

Fig. 2-2-1

|     | Connection  |                  |         |        |             | Parts Number |                |  |

|-----|-------------|------------------|---------|--------|-------------|--------------|----------------|--|

| 1   | MAIN CN4001 | ←→ OPRATION UNIT |         | 12     | YTU94077-12 | FPC wire     |                |  |

|     |             |                  |         |        |             | YTU94074-12  | FPC CN.ASSY    |  |

| 2   | MAIN        | <b>←→</b>        | MON/REG | CN9001 | 80          | YTU94126B-80 | B TO B CN.ASSY |  |

| 3   | MAIN CN2001 | <b>←</b> →       | CCD     | CN1001 | 28          | YTU94077-28  | FPC wire       |  |

| 4   | MAIN CN5501 | <b>←</b> →       | JACK    | CN101  | 38          | YTU94077-38  | FPC wire       |  |

| (5) | MAIN CN501  | <b>←→</b>        | OPUNIT  |        | 22          | YTU94077-22  | FPC wire       |  |